# 3-D Construction of Monolithic Passive Components for RF and Microwave ICs Using Thick-Metal Surface Micromachining Technology

Jun-Bo Yoon, *Member, IEEE*, Byeong-Il Kim, *Member, IEEE*, Yun-Seok Choi, and Euisik Yoon, *Member, IEEE*

**Abstract**—As a viable technological option to address today's strong demands for high-performance monolithic low-cost passive components in RF and microwave integrated circuits (ICs), a new CMOS-compatible versatile thick-metal surface micromachining technology has been developed. This technology enables to build arbitrary three-dimensional (3-D) metal microstructures on standard silicon substrate as post-IC processes at low temperature below 120 °C. Using this technology, various highly suspended 3-D microstructures have been successfully demonstrated for RF and microwave IC applications. We have demonstrated spiral inductors suspended 100  $\mu\text{m}$  over the substrate, coplanar waveguides suspended 50  $\mu\text{m}$  over the substrate, and complicated microcoaxial lines, which have 50- $\mu\text{m}$ -suspended center signal lines surrounded by inclined ground shields of 100  $\mu\text{m}$  in height. The microwave performance of the microcoaxial transmission line fabricated on a glass substrate has been evaluated to achieve very low attenuation of 0.03 dB/mm at 10 GHz with an effective dielectric constant of 1.6. The process variation/manufacturability, mechanical stability, and package issues also have been discussed in detail.

**Index Terms**—Coaxial transmission lines, coplanar microstrip lines, high- $Q$ , inductors, RF and microwave microelectromechanical systems (MEMS), silicon RF integrated circuits (ICs), surface micromachining, three-dimensional (3-D) micromachined passive components.

## I. INTRODUCTION

RECENT STRONG demands on high-performance monolithic low-cost passive components in RF and microwave integrated circuits (ICs) have driven researchers to find out alternative technical options to enhance the performance of passive components acquired from conventional thin-film planar IC technologies. From this perspective, various micromachining technologies developed for microelectromechanical systems (MEMS) have been also spotlighted in the fields of RF and microwave ICs as a promising technological option to achieve more than an order of magnitude improvement in size, cost, and performance [1]–[4].

Bulk micromachining, which etches bulk substrate in order to remove lossy substrate under high-frequency signal lines, has been utilized in fabricating monolithic RF/microwave

inductors [5]–[9], microwave/millimeter-wave transmission lines [10]–[12], and filters [13], [14]. Surface micromachining, which does not etch the substrate, but deposits a thick insulating layer or a sacrificial layer on the substrate to isolate suspended (sometimes movable) structural layers from the lossy substrate, has been utilized in fabricating three-dimensional (3-D) solenoid inductors [15]–[20], spiral inductors [21], [22], suspended spiral inductors [23]–[27], RF/microwave tunable capacitors [2], [28]–[30], millimeter-wave tunable filters [31], microwave/millimeter-wave transmission lines [21], [32], [33], and RF/microwave switches (well summarized in [2]). Also, LIGA, which is a German acronym of Lithographie (X-ray lithography), Galvanoformung (electroplating), and Abformung (molding), has been utilized to form high-aspect-ratio metal microstructures for transmission lines and filters [34]. Porous silicon has also been applied to produce inductors [35], [36] and coplanar waveguides (CPWs) [37]. Table I summarizes the performance of various bulk/surface-micromachined RF inductors fabricated on a silicon substrate. Although bulk micromachining opened the MEMS era, there have been restrictions on process/package compatibility and structural arbitrariness associated with the substrate etching. This may be the reason why we can find surface-micromachined passive components preferably used for circuit integration in many recent papers [2], [20], [22], [28], [29].

As a technique to build microstructures on the top of substrate, thick-metal surface micromachining has been investigated during the last decade, based on LIGA and LIGA-like technologies [38]–[41]. It consists of fabrication of molds followed by electroplating. As a mold for an electroplating guide, various materials have been investigated. Electron-beam-sensitive polymethylmethacrylate (PMMA) resist [38] has been applied to transmission lines and filters [34]. UV-sensitive polyimide [39] has been used to build inductors [16], [23], [24], [26] and filters [24]. Conventional positive thick photoresist [40], [41] have been utilized for inductors [17]–[19], [25], [27] and CPW lines [33]. Epoxy-based negative thick photoresist [42] has been also utilized for inductors [20]. Among these, the conventional positive thick photoresist is the most convenient one to use in terms of process simplicity, process time, and compatibility. Instead of multistacking two-dimensional (2-D) molds and metal to fabricate 3-D microstructures [16], [23], [24], [26], [43], there has been an approach to realize 3-D photoresist molds directly in order to obtain 3-D metal microstructure at once [44]. This method has been applied to solenoid inductors [17]–[19]. Instead of polymer-based molds,

Manuscript received November 1, 2001. This work was supported by the Ministry of Science and Technology, Korea, under a National Research Laboratory grant.

The authors are with the Division of Electrical Engineering, Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea (e-mail: jbyoon@ee.kaist.ac.kr).

Digital Object Identifier 10.1109/TMTT.2002.806511

TABLE I

PERFORMANCE SUMMARY OF THE VARIOUS BULK/SURFACE MICROMACHINED RF INDUCTORS FABRICATED ON SILICON

| Feature                          | Bulk micromachining |                    |                   |                 |                          |                  | Surface micromachining |           |           |                     |             |                  |           |                        |

|----------------------------------|---------------------|--------------------|-------------------|-----------------|--------------------------|------------------|------------------------|-----------|-----------|---------------------|-------------|------------------|-----------|------------------------|

|                                  | Spiral              |                    |                   |                 | Spiral on porous silicon |                  | Solenoid               |           |           | Spiral on polyimide |             | Suspended spiral |           |                        |

| Primary author                   | Chang [5]           | Chi [6]            | Lu [7]            | Jiang [9]       | Nam [35]                 | Kim [36]         | Young [15]             | Yoon [19] | Chen [20] | Kim [21]            | Rogers [22] | Park [26]        | Yoon [27] | Yoon [51] <sup>f</sup> |

| Year                             | 1993                | 1994               | 2000              | 2000            | 1997                     | 2001             | 1997                   | 1999      | 2001      | 1995                | 2001        | 1999             | 1999      | 2001                   |

| Silicon substrate resistivity    | Low                 | High               | High <sup>g</sup> | Si <sup>c</sup> | Low                      | Low              | Low                    | Si        | Low       | Si                  | Low         | Low              | Low       | Low                    |

| Inductance (nH)                  | 100                 | 1.2                | 1.8               | 2.7             | 6.3                      | 5.7              | 4.8                    | 2.7       | 2.6       | 10                  | 2.6         | 16               | 1.8       | 1.4                    |

| Peak $Q^a$                       | n/a                 | 50-60 <sup>e</sup> | 20.2              | 36 <sup>b</sup> | 13.3                     | 29               | 30                     | 17        | 21        | 5.5                 | 17          | 16               | 50        | 70                     |

| Peak- $Q$ frequency (GHz)        | n/a                 | 30-40 <sup>e</sup> | 14.5              | 5.2             | 4.6                      | 7                | 1                      | 2.4       | 4.5       | 1.2                 | 2.5         | 0.1              | 7         | 6                      |

| Self resonant frequency (GHz)    | 3 <sup>e</sup>      | 70 <sup>e</sup>    | 25.6              | 6.6             | 13.8                     | >20              | >4                     | >10       | >10       | 6                   | n/a         | >2               | >10       | >20                    |

| $Q^a$ @ 1GHz                     | 4 <sup>e</sup>      | n/a                | 4                 | 3               | 4                        | 4                | 30                     | 12        | 10        | 5                   | n/a         | 4                | 22        | 32                     |

| $Q^a$ @ 5GHz                     | n/a                 | n/a                | 13                | 36 <sup>b</sup> | 13                       | 20               | n/a                    | 12        | 19        | 1                   | n/a         | n/a              | 45        | 63                     |

| Etch substrate?                  | Y                   | Y                  | Y                 | Y               | Y                        | Y                | N                      | N         | N         | N                   | N           | N                | N         | N                      |

| Post-IC compatible?              | Y                   | Y                  | Y                 | N               | N                        | Y/N <sup>d</sup> | Y                      | Y         | Y         | Y                   | Y           | Y                | Y         | Y                      |

| Maximum process temperature (°C) | <120                | <120               | <120              | 1150            | 1120                     | 300              | 170                    | 120       | <120      | 350                 | 350         | 350              | 120       | 120                    |

<sup>a</sup> defined by conventional  $Q = \text{Im}[1/Y_{11}]/\text{Re}[1/Y_{11}]$

<sup>b</sup>  $Q$  increased abruptly before peak  $Q$

<sup>c</sup> susceptible to Cu contamination since Cu deposited on silicon without any diffusion barrier

<sup>d</sup> subject to substrate type and resistivity (p+ silicon, 0.007Ω·cm) for the porous process

<sup>e</sup> expected value

<sup>f</sup> using the fabrication technology developed in this work

<sup>g</sup> Si/SiGe

a sacrificial metal mold has also been reported [45] and applied to fabricate inductors [25], [27] and transformers [46].

In this paper, we report the thick-metal surface micromachining technology that we have developed recently [47], its process details, and microwave measurement results of the fabricated 3-D microstructure. This recent development is based on the multiexposure single development (MESD) method reported in [17] and [44]. In this paper, we have developed a new fabrication process to improve the MESD method, so that we can overcome the major drawback of the previous approach (size limit in the suspended structure) and enable to build arbitrary shapes of highly suspended thick-metal microstructures. This technology is fully CMOS compatible and can be integrated as post-IC processes. In this paper, we report on the fabrication technology as a viable construction tool enabling monolithic integration of versatile 3-D metal microstructures suitable for high-performance RF/microwave/millimeter-wave passive components.

## II. FABRICATION

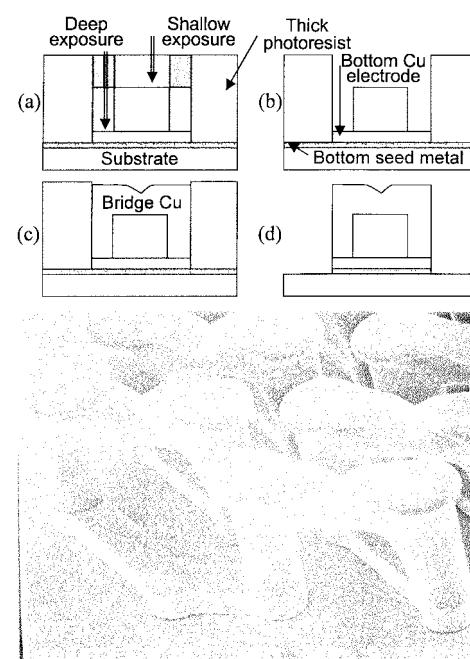

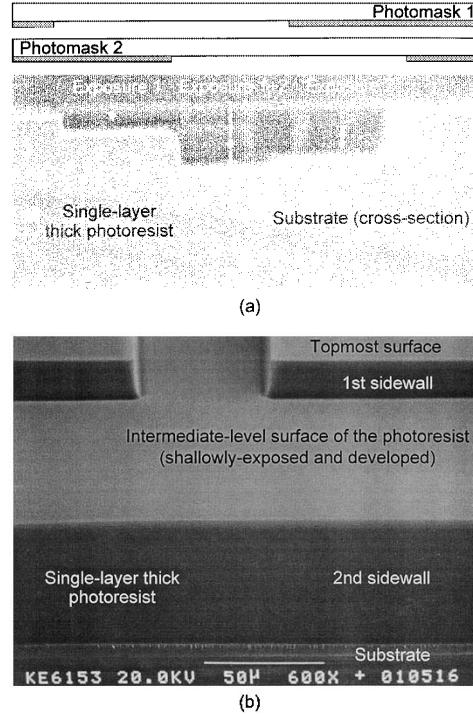

Fig. 1 shows the original MESD method on which the new fabrication technology in this paper is based [17], [44]. The process starts with a substrate on which the bottom seed metal is deposited. The bottom Cu electrode is then formed by the conventional lithography with a thick photoresist followed by electroplating. After removing the photoresist, another thick photoresist is spun on the wafer. In Fig. 1(a), a two-step exposure

Fig. 1. Original MESD technology [17] process steps and the fabricated solenoid structure. (a) Double exposure. (b) Single development. (c) Bridge electroplating. (d) Photoresist removal. The bridge is completed by the lateral overflow of the electroplated metal during the bridge electroplating.

is done on the photoresist using two different photomasks (each mask has different exposure times) to leave a 3-D latent image.

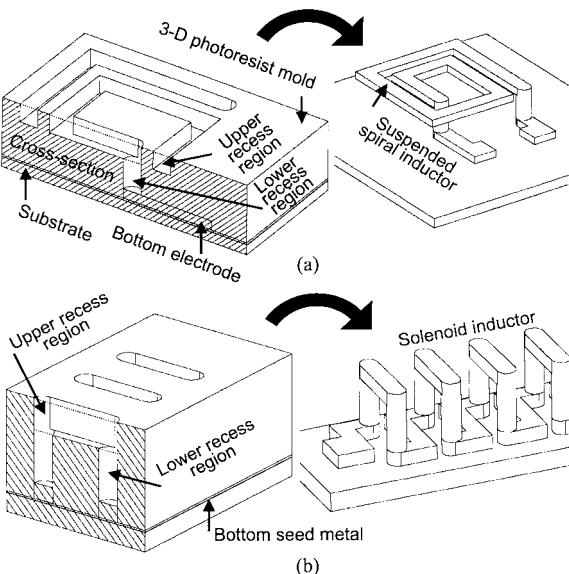

Fig. 2. Brief schematic presentation of the proposed 3-D thick-metal surface micromachining technology. The 3-D photoresist mold and fabricated metal structure have been presented for: (a) suspended spiral inductor and (b) solenoid inductor. The process is simply composed of the 3-D photoresist mold fabrication, metal filling in lower and upper recess regions, and removing the photoresist mold.

After the single-step development, the 3-D photoresist mold is revealed, as shown in Fig. 1(b). This is why we named this technology as MESD. Single-step electroplating is then employed to form the single-body air bridges, as shown in Fig. 1(c). After removing the photoresist and etching the seed metal, the solenoid structure is obtained, as shown in Fig. 1.

The reason why we use the shallow exposure mask instead of building the bridge directly on top of the photoresist is due to difficulties in such a process. In order to form the electroplated bridge on the top of the lower photoresist, we need to deposit an additional seed metal layer on the lower photoresist prior to the lithography step to define the bridge photoresist mold. During the second bridge mold lithography, the lower thick photoresist is liable to be deformed from the thermal cycle of photoresist baking, resulting in significant degradation in the whole process yield.

In the original MESD method, the bridge is completed by overplating (overflow of the electroplating), i.e., the bridge metal is sequentially grown to fill holes, overflow laterally, and finally form completely connected bridges. However, this method has a limit in bridge length since overplating takes place not only laterally, but also upwards equally. Therefore, very limited application areas were unavoidable, such as small-size solenoids [17]–[19] and 3-D nozzle plates in a monolithic inkjet printhead [48].

Fig. 2 shows a schematic of the new 3-D thick-metal surface micromachining technology. First, we make a 3-D photoresist mold having arbitrarily shaped upper recess regions, as shown in Fig. 2. Second, we fill both lower/upper recess regions with metal. Finally, we remove the photoresist molds. The fabrication process of this structure is illustrated in Fig. 3. The left-hand side of this figure shows the process steps for suspended inductors, the right-hand side for solenoids. The cross-sectional schematics in Fig. 3 correspond to those areas indi-

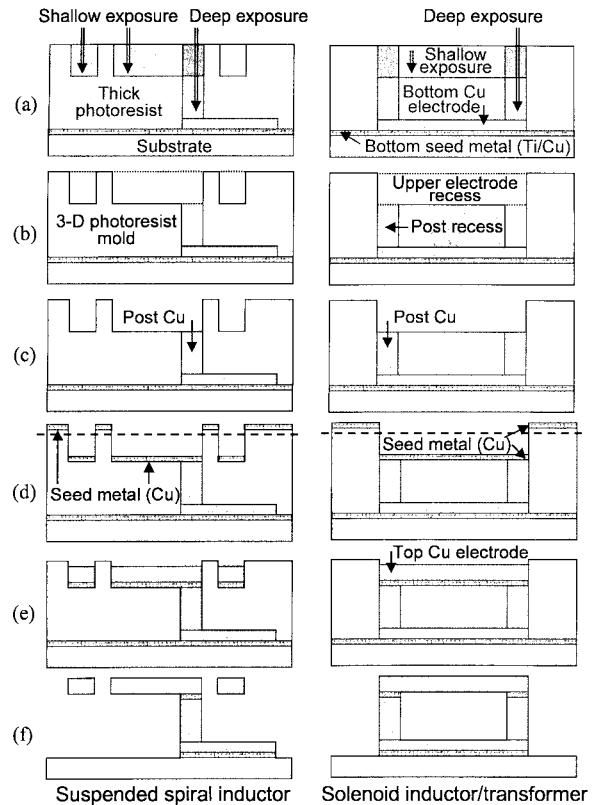

Fig. 3. Schematic cross-sectional views of the proposed fabrication process flow for the suspended-spiral and solenoid inductors. (a) Double exposure. (b) Single development. (c) Post electroplating. (d) Second seed metal deposition. (e) Mechanical polishing of the topmost second seed metal and upper electrode electroplating. (f) Removing the photoresist to release the structure.

cated in Fig. 2. Note that the two posts in the solenoid are located far from each other to show the difference explicitly from the original MESD process.

Up to the steps in Fig. 3(b), the process is identical to the original MESD method. The substrate is a 4-in standard silicon wafer covered by 1- $\mu\text{m}$ -thick thermal oxide for electrical isolation. The bottom seed metal is composed of 2000- $\text{\AA}$ -thick Cu over 200- $\text{\AA}$ -thick Ti, in which the Ti is utilized as an adhesion promoter, as well as a diffusion barrier for Cu. The thickness of the photoresist ranges from 10 to 65  $\mu\text{m}$  depending on spin-coating conditions. We have already reported the process details for the high-aspect-ratio ( $>10$ ) lithography with a 20–90- $\mu\text{m}$ -thick AZ9262 photoresist from Clariant [49]. The typical MESD process conditions can be found in [17].

Once the 3-D photoresist mold is fabricated, the lower recess region is filled with the electroplated metal to form the posts in Fig. 3(c). The Cu electroplating solution used in this study has been reported in detail in [17]. The Cu electroplating has been done at room temperature. Since the post electroplating is done filling upward from the bottom of the lower recess region, we can obtain fully filled robust posts.

After the post electroplating, second seed metal is deposited on the entire wafer surface, as shown in Fig. 3(d). In order to ensure the next electroplating occurs only in the upper recess region, the topmost surface of the second seed metal is removed. We have successfully removed the seed layer using me-

chanical polishing. We have used a conventional polishing machine, which is commercially available and normally used for preparing material specimen. The dashed line shown in Fig. 3(d) indicates the boundary to which the mechanical polishing is done. The polishing depth has been controlled by setting time from the initial experiments. This little change makes the whole process very different from the original work.

Next, another electroplating is performed to fill the upper recess regions with metal, as shown in Fig. 3(e). Since all second seed metal in the upper recess regions are electrically connected to the bottom seed metal through the metal posts, all the upper recess regions are simultaneously filled during the electroplating. This makes it possible to obtain longer and arbitrarily shaped suspended structures. Note that the upper recess region should not be isolated, which means it must be designed to overlap with at least one lower recess region in order to be electrically connected to the bottom seed metal; hence, to be electroplated.

Finally, the 3-D photoresist mold is selectively etched away in acetone by wet immersion and the bottom seed metal is etched for electrical isolation between devices. Since the bottom seed metal is composed of Cu, which is the same material as the structure, there has been a little loss in the structural thickness during the seed-metal etching. However, the loss is negligible. Now, the suspended structure is released, as shown in Fig. 3(f).

### III. RESULTS AND DISCUSSION

#### A. Process Variation and Manufacturability

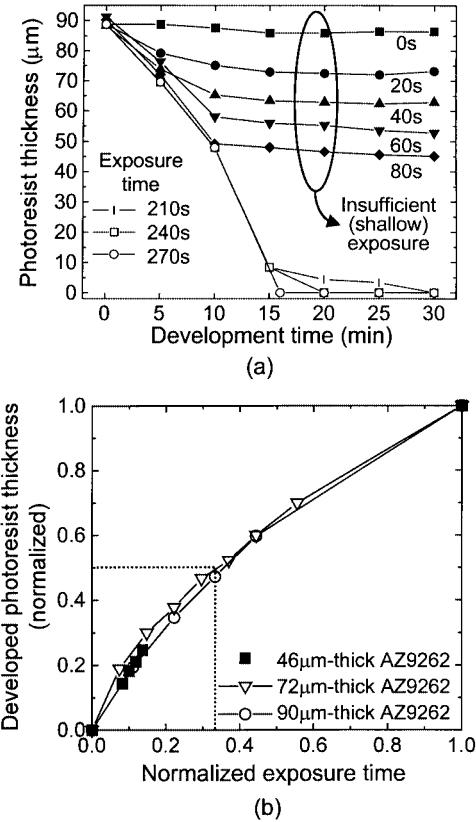

As can be seen in Fig. 3(a) and 3(b), the suspension height of the suspended metal structure is determined by the original photoresist thickness minus the shallow-exposure depth. In order to obtain the process variation of the suspension height, a couple of considerations have been addressed. The uniformity of the photoresist film thickness has been obtained within  $\pm 5\%$  for a single coating of the 90- $\mu\text{m}$ -thick photoresist over a 4-in wafer excluding thick edge beads [17]. We have used a conventional contact mask aligner, which has typical UV intensities of 10 and 15  $\text{mW/cm}^2$  at 365- and 405-nm wavelengths, respectively, with the light uniformity of  $\pm 5\%$  over a 6-in beam area. The shallow-exposure depth has been controlled by exposure time utilizing the characteristics that the development is stopped (saturated) to a certain depth in the photoresist when the exposure is insufficient. This has been well characterized, as can be seen in Fig. 4(a). The shallow-exposure depth increases as the exposure time gets longer in a common fashion regardless of the initial photoresist thickness, as shown in Fig. 4(b). Therefore, once the initial photoresist thickness has been known, we can set the shallow-exposure time according to the normalized characteristic shown in Fig. 4(b). For example, we need one-third of the full-exposure time to obtain one-half of the initial photoresist thickness.

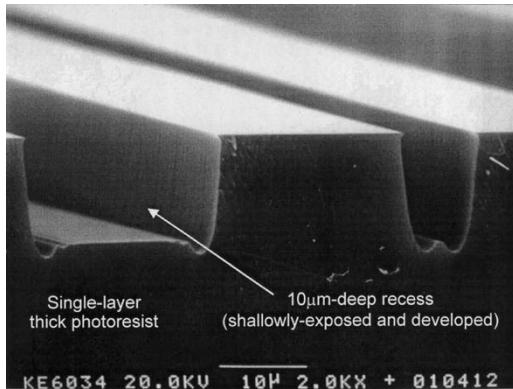

Fig. 5 shows the SEM microphotographs of the 3-D photoresist mold fabricated by the proposed MESD method. Although we have utilized only a single intermediate level within the photoresist, as shown in Fig. 3(b), Fig. 5(a) shows that we can obtain dual intermediate levels within the photoresist by utilizing

Fig. 4. Lithographic development characteristics of the positive thick photoresist AZ9262 [17] with: (a) various insufficient/sufficient exposure times and (b) normalized exposure times. The shallow-exposure depth shows a common fashion regardless of the initial photoresist thickness when the exposure conditions are adequately normalized.

Fig. 5. SEM microphotographs of the 3-D photoresist mold fabricated by the proposed MESD method. (a) Cross-sectional view showing dual intermediate levels within a single-layer photoresist (relevant photomasks also illustrated). (b) Perspective view showing very smooth intermediate-level surface of the single-layer photoresist.

Fig. 6. SEM microphotograph of the fabricated 10- $\mu$ m-deep recess within the single-layer photoresist.

the overlapped exposure. The relevant photomasks has been shown in the figure as well. This may increase the 3-D versatility of this technology for obtaining more complicated microstructures. Fig. 5(b) is provided to investigate the surface smoothness of the intermediate level within the single-layer photoresist before the second seed metal is deposited. We have not observed any changes in surface smoothness before and after the second seed metal deposition. Note that the SEM specimen is already coated by 500- $\text{\AA}$  sputtered Au as usual. Fig. 6 shows the magnified cross-sectional view of the 10- $\mu$ m-deep recess within the single-layer photoresist in which the recess region is made by the shallow exposure and development. We have observed UV intensification at the pattern edges that might come from the scattering/diffraction phenomena at the edges, as can be clearly seen in Fig. 6. As a pattern size shrinks down below 5  $\mu$ m, the shallow-exposure depth starts to deviate from the usual depth and is decreased.

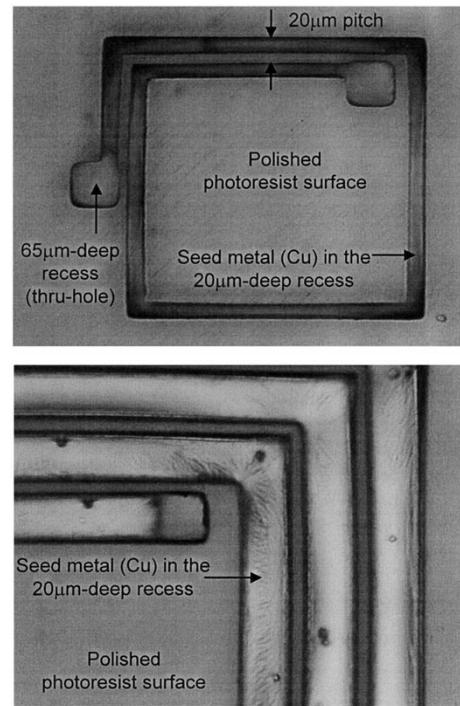

The polished surface of the topmost photoresist has been another important issue to be investigated. In Fig. 7, the top surface of the photoresist after polishing the second seed metal has remained in good shape. No residue of the second seed metal has been observed, no surface photoresist structure [20- $\mu$ m-deep 10- $\mu$ m-line/space structure in Fig. 7(a)] has been damaged and the second seed metal on the bottom of the upper recess regions has remained well.

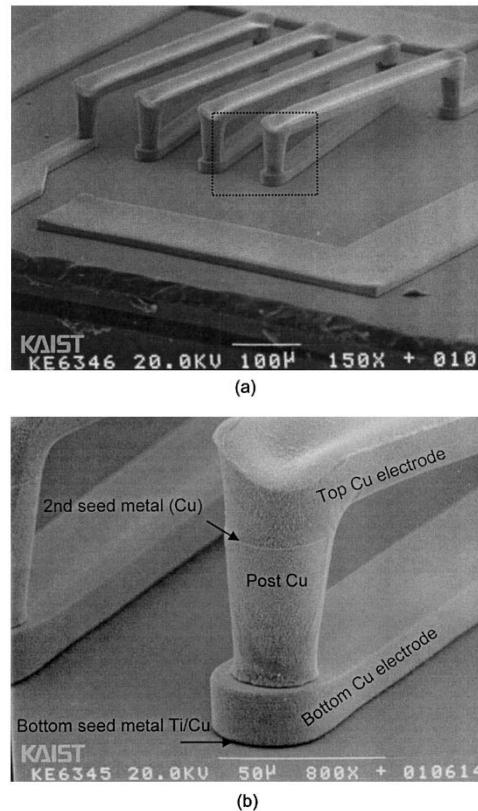

Fig. 8 demonstrates the fabricated solenoid structure with very long bridges, which clearly could not be made by the original MESD process [17]. Also, the robust post structure can be made. Note that, owing to the excellent planarization capability of the sacrificial photoresist mold, we cannot observe any marks of the bottom electrodes imprinted onto the upper suspended electrodes. This was not the case in our previous work [45], in which electroplated metal was used as the sacrificial layer, instead of spin-coated photoresist.

The thickness of the suspended structure has been determined to ensure the structural robustness and RF performance. According to our experiments, at least 10  $\mu$ m in thickness should be maintained in order to minimize any structural deformation during the fabrication process, as well as to achieve a high quality factor. We have observed that the quality factor ( $Q$ ) of the inductors starts to be saturated at the thickness of 10  $\mu$ m and there is little increment in  $Q$  beyond 15  $\mu$ m.

Fig. 7. Optical microphotographs of the polished photoresist surface taken after the topmost second seed metal has been removed by the mechanical polishing.

Fig. 8. SEM microphotographs of the fabricated solenoid structures. (a) Bird's-eye view. (b) Magnified view of the post structure. Such long bridges can be successfully fabricated with robust formation of the posts.

The process variation in the electroplating thickness has been achieved within  $\pm 15\%$  using a lab-made electroplating appa-

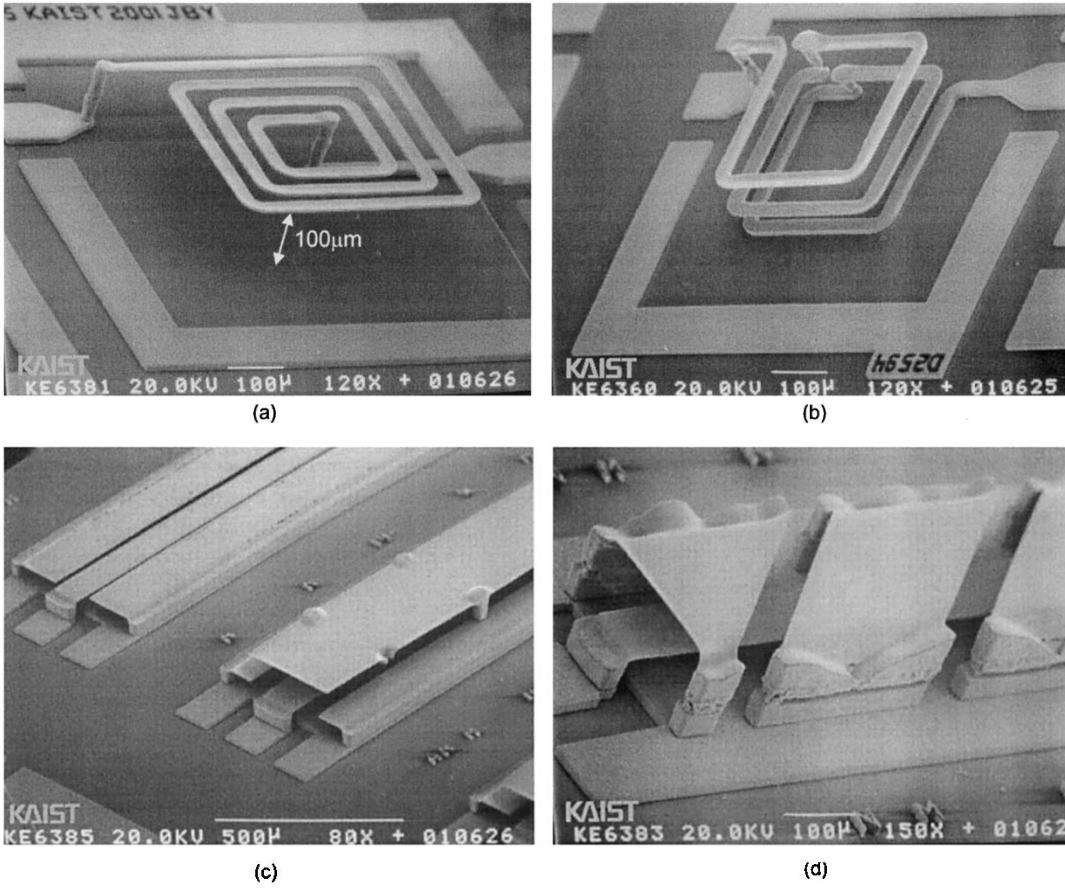

Fig. 9. SEM microphotographs of the fabricated RF inductors and microwave/millimeter-wave transmission lines. (a) Spiral inductor suspended by  $100 \mu\text{m}$  over the substrate fabricated using a repetition of the fundamental process shown in Fig. 3. (b) Vertical solenoid inductor. (c) Coplanar microstrip line (left-hand side) and the same structure with a cover shield (right-hand side). (d) Microcoaxial transmission line with inclined shields.

ratus and solution. However, this can be improved by uniform pattern distribution in the wafer and employing a commercial electroplating machine and process. For RF inductor applications, the amount of the thickness variation corresponds to the inductance variation of up to  $\pm 3\%$  [50].

We have obtained the whole process yield of over 90% among 4000 inductors fabricated in the 4-in wafer in our university fabrication facility, which makes the technology fairly manufacturable. All the process temperature has been below  $120^\circ\text{C}$ , which makes it possible to integrate our surface-micromachined passive components onto the wafer that has finished the IC process.

### B. Structural Variations

Fig. 9 shows the SEM microphotographs of the various inductors and transmission lines fabricated by using the proposed technology. From all the structures in Fig. 9, one can see that they have been easily shaped in many variations and suspended flat, due to the excellent planarization capability of the sacrificial photoresist mold. The flat suspended lines also indicate no internal stress gradient residing in the electroplated metal structures. All the suspended inductors have been successfully supported by only a few posts (typically two). In Fig. 9, we have demonstrated spiral inductors suspended  $100 \mu\text{m}$  over the substrate, CPWs suspended  $50 \mu\text{m}$  over the substrate, and complicated microcoaxial lines, which has  $50\text{-}\mu\text{m}$  suspended center

signal lines surrounded by inclined ground shields of  $100 \mu\text{m}$  in height.

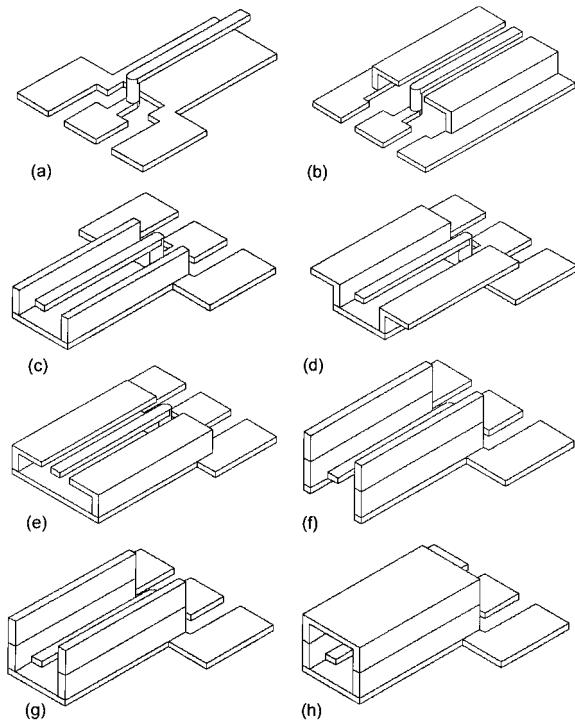

The multilevel microstructures in Fig. 9(a)–(d) have been made by a repetition of the fundamental process shown in Fig. 3. This demonstrates that our technology is versatile to construct multilevel fairly complicated microstructures, such as the 3-D microcoaxial transmission line with inclined shields in Fig. 9(d). The inclined shield in Fig. 9(d) has been adopted for enhancing the sacrificial photoresist etch, however, this is not mandatory. Fig. 10 also illustrates schematic examples of various 3-D transmission lines that can be constructed by this technology.

### C. RF/Microwave Measurement

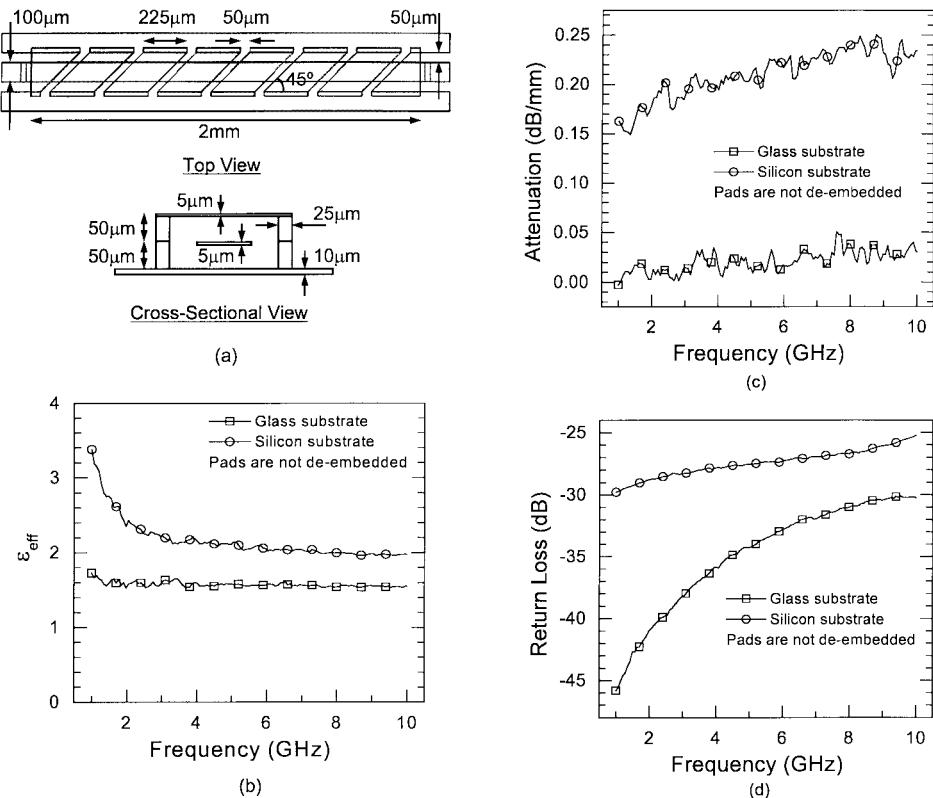

Among the fabricated 3-D microstructures, the microcoaxial transmission line shown in Fig. 9(d) has been electrically characterized. The physical dimensions of the device are illustrated in Fig. 11(a). The on-wafer microwave measurement has been performed from 1 to 10 GHz using an HP8720C network analyzer, coplanar ground–signal–ground (GSG) probes, and a microwave probing station. The full two-port calibration including short, open, load, and thru (SOLT) has been done using a GGB Industries CS-5 calibration kit. 4-in glass and low-resistivity ( $1\sim 30 \Omega \cdot \text{cm}$ ) silicon substrates were used on which the identical microcoaxial transmission lines were fabricated during the simultaneous run. For silicon substrate,

Fig. 10. Schematic examples of various 3-D microwave/millimeter-wave transmission lines, which can be realized by using the proposed 3-D microconstruction technology. (a) Microstrip line. (b) Suspended coplanar line. (c) Sidewall-shielded microstrip line. (d) Bottom-shielded suspended coplanar line. (e) Coplanar microstrip line. (f) Sandwiched microstrip line. (g) Semicoaxial line. (h) Microcoaxial line.

1- $\mu\text{m}$ -thick thermal oxide was covered for electrical isolation. Note that the  $100\ \mu\text{m} \times 125\ \mu\text{m}$  pads were not deembedded. The simulated characteristic impedance of the microcoaxial transmission line was  $39\ \Omega$  at the design stage. Fig. 11(b)–(d) shows the measured effective dielectric constant, attenuation, and return loss of the fabricated microcoaxial transmission line, respectively, each of which shows the performance of both on-glass and on-silicon devices for comparison. A very low attenuation of  $0.03\ \text{dB/mm}$  at  $10\ \text{GHz}$  has been obtained from the on-glass microcoaxial transmission line, whereas  $0.24\ \text{dB/mm}$  was observed from the on-silicon device. Also, a very low and nearly flat effective dielectric constant of  $1.6$  for all measured frequency ranges has been observed from the on-glass device, whereas  $2.0$  and greater was observed from the on-silicon device. We believe that there will be much improvement on the performance of the on-silicon device should the pad deembedding is performed since the pads occupy a large area in intimate contact with the lossy silicon substrate. Both devices have shown their return loss less than  $-25\ \text{dB}$  up to  $10\ \text{GHz}$ , indicating very good matching with the current device dimensions.

Since the structure height is very high compared with that achievable from the conventional technologies and air is used as a medium with the lowest dielectric constant, we can achieve low ohmic loss (or attenuation) along with wider signal lines, a low effective dielectric constant, and low radiation loss.

The RF performance of the suspended inductors fabricated by this technology was reported elsewhere [51], however,

the representative data are listed in the right-most column of Table I.

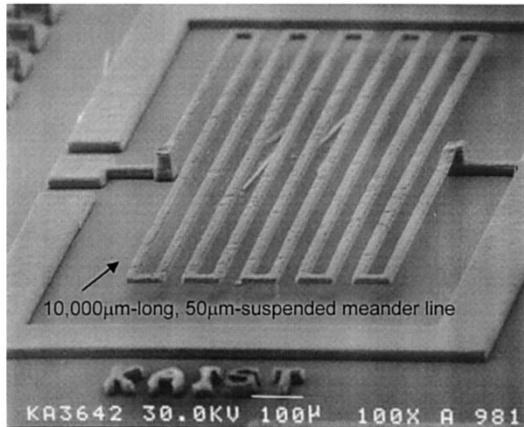

#### D. Mechanical Stability and Packaging

The suspended microstructures seem to be mechanically vulnerable at the first glance against shock and vibration. However, we have observed several evidences showing that it is not true. Note that in the micrometer regime, any gravity-related phenomenon diminishes rapidly. This is why we cannot observe any bending by the gravity within the freestanding microstructures in Fig. 9(a) and 9(b). Actually, MEMS structures utilize this phenomenon actively. In this sense, Fig. 12 shows one example. A  $10\,000\text{-}\mu\text{m}$ -long meander line is suspended by  $50\ \mu\text{m}$  above the substrate without any structural deformation and instability. This structure has survived throughout all the standard routine processes including dipping, rinsing, and blowing. Also, occasional chip-dropping tests during the SEM photo job have shown no damage in the suspended structure. In fact, the imperfect, vulnerable structure in Fig. 9(b) also has passed through the fabrication and SEM jobs with negligible structural deformation. However, the structural robustness needs to be substantiated by rigorous industrial mechanical reliability tests including shock and vibration.

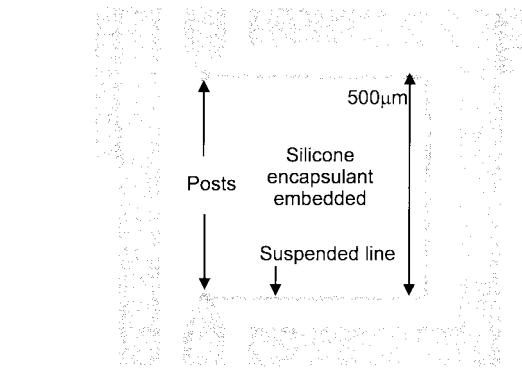

As one possible solution for the mechanical reliability and packaging compatibility, we have investigated the encapsulation of the suspended microstructure in silicone encapsulant. This material is commercially available for use in reliable protection of sensitive circuits and components (Sylgard 184 from Dow Corning). The encapsulant has been spin coated into the finished and freestanding microstructures. Fig. 13 shows the encapsulant-embedded structure of the  $1500\text{-}\mu\text{m}$ -long line suspended from the substrate by  $50\ \mu\text{m}$ . It is easily observed (the encapsulant is transparent) that this structure maintains its original shape without any deformation. This is because the suspended-line microstructures can be considered as a bond wire, which has been already proven to be well encapsulated in the common plastic packaging. Note that Cu used as the structural material in this study is more robust than Au of which the bond-wire is made, and the structure in this study has a comparable diameter to the bond wire. Sometimes people utilize bond-wire inductors for achieving high- $Q$  factors in silicon RF ICs, which has a nominal vertical distance of  $150\ \mu\text{m}$  from the substrate [52]. The most difficult problem in this approach is the inductance variation and its reproducibility due to the shape variation of the bond wire. Using our technology, we can replace the bond-wire inductors with very accurately shaped (since defined by lithography) reproducibly fabricated and batch-fabricated high- $Q$  suspended inductors, which are also rigid enough to be safely encapsulated in conventional encapsulating materials. Additionally, large pad areas (typically  $>80\ \mu\text{m} \times 80\ \mu\text{m}$  each) required in the bond-wired inductors can be significantly saved in our proposed structure. However, it is required to study the performance degradation after encapsulation, which comes from the finite dielectric constant and loss tangent of the encapsulation material. (e.g., the silicone encapsulant has a dielectric constant of  $2.65$  and a loss tangent less than  $0.001$ ).

Fig. 11. Microwave characteristics of the fabricated microcoaxial transmission line shown in Fig. 9(d), fabricated on glass and standard silicon substrates. (a) Schematic views. (b) Effective dielectric constant. (c) Attenuation. (d) Return loss of the microcoaxial transmission line.

Fig. 12. SEM microphotograph of the 10 000- $\mu$ m-long 50- $\mu$ m-suspended meander line. This structure has survived throughout all the standard routine processes such as dipping, rinsing, and blowing.

#### IV. CONCLUSIONS

The new thick-metal surface micromachining technology has been developed with strong emphasis on structural robustness, versatility, and reliability and CMOS compatibility and process manufacturability. We have successfully fabricated various microstructures for RF and microwave passives including suspended spiral inductors, solenoid inductors, transformers, suspended CPWs, and microcoaxial transmission lines at a low temperature below 120 °C. The proposed technology can extend the limit in the degree of freedom residing in the current planar IC technologies and can enhance the performance of

Fig. 13. Optical microphotograph of the 1500- $\mu$ m-long 50- $\mu$ m-suspended inductor microstructure embedded in the spin-coated transparent commercial silicone encapsulant.

integrated RF ICs. Process variations, as well as structural stability and packaging issues of the proposed technology, have been discussed extensively with the details of fabrication processes. We have demonstrated that this technology can provide a viable manufacturing option for monolithic integration of high-performance RF/millimeter-wave passive components.

#### ACKNOWLEDGMENT

The authors would like to thank I.-J. Cho, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, and B.-G. Kim, KAIST, for taking SEM pictures. All fabrication has been done at the Semiconductor Laboratory, KAIST.

## REFERENCES

- [1] C. T.-C. Nguyen, L. P. B. Katehi, and G. M. Rebeiz, "Micromachined devices for wireless communications," *Proc. IEEE*, vol. 86, pp. 1756–1768, Aug. 1998.

- [2] J. J. Yao, "RF MEMS from a device perspective," *J. Micromech. Microeng.*, vol. 10, pp. R9–R38, Dec. 2000.

- [3] R. J. Richards and H. J. De Los Santos, "MEMS for RF/microwave wireless applications: The next wave," *Microwave J.*, vol. 44, pp. 20–41, Mar. 2001.

- [4] L. P. B. Katehi, J. F. Harvey, and K. J. Herrick, "3-D integration of RF circuits using Si micromachining," *IEEE Microwave Mag.*, vol. 2, pp. 30–39, Mar. 2001.

- [5] J. Y.-C. Chang, A. A. Abidi, and M. Gaitan, "Large suspended inductors on silicon and their use in a 2- $\mu$ m CMOS RF amplifier," *IEEE Electron Device Lett.*, vol. 14, pp. 246–248, May 1993.

- [6] C.-Y. Chi and G. M. Rebeiz, "Planar millimeter-wave microstrip lumped elements using micro-machining techniques," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1994, pp. 657–660.

- [7] L.-H. Lu, G. E. Ponchak, P. Bhattacharya, and L. P. B. Katehi, "High- $Q$   $X$ -band and  $K$ -band micromachined spiral inductors for use in Si-based integrated circuits," in *IEEE Topical Silicon Monolithic Integrated Circuits in RF Syst. Meeting Dig.*, Sept. 2000, pp. 108–112.

- [8] R. P. Ribas, J. Lescot, J.-L. Leclercq, J. M. Karam, and F. Ndagijimana, "Micromachined microwave planar spiral inductors and transformers," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 1326–1335, Aug. 2000.

- [9] H. Jiang, Y. Wang, J.-L. A. Yeh, and N. C. Tien, "On-chip spiral inductors suspended over deep copper-lined cavities," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 2415–2423, Dec. 2000.

- [10] L. P. B. Katehi, G. M. Rebeiz, T. M. Weller, R. F. Drayton, H. J. Cheng, and J. F. Whitaker, "Micromachined circuits for millimeter- and sub-millimeter-wave applications," *IEEE Antennas Propagat. Mag.*, vol. 35, pp. 9–17, Oct. 1993.

- [11] V. Milanovic, M. Gaitan, E. D. Bowen, and M. E. Zaghoul, "Micromachined coplanar waveguides in CMOS technology," *IEEE Microwave Guided Wave Lett.*, vol. 6, pp. 380–382, Oct. 1996.

- [12] K. J. Herrick, T. A. Schwarz, and L. P. B. Katehi, "Si-micromachined coplanar waveguides for use in high-frequency circuits," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 762–768, June 1998.

- [13] C.-Y. Chi and G. M. Rebeiz, "Planar microwave and millimeter-wave lumped elements and coupled-line filters using micro-machining techniques," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 730–738, Apr. 1995.

- [14] S. V. Robertson, L. P. B. Katehi, and G. M. Rebeiz, "Micromachined  $W$ -band filters," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 598–606, Apr. 1996.

- [15] D. J. Young, V. Malba, J.-J. Ou, A. F. Bernhardt, and B. E. Boser, "Monolithic high-performance three-dimensional coil inductors for wireless communication applications," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Dec. 1997, pp. 67–70.

- [16] Y.-J. Kim and M. G. Allen, "Surface micromachined solenoid inductors for high frequency applications," *IEEE Trans. Comp. Packag. Manufact. Technol.*, vol. 21, pp. 26–33, Jan. 1998.

- [17] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "Monolithic fabrication of electroplated solenoid inductors using three-dimensional photolithography of a thick photoresist," *Jpn. J. Appl. Phys.*, pt. 1, vol. 37, no. 12B, pp. 7081–7085, Dec. 1998.

- [18] J.-B. Yoon, B.-K. Kim, C.-H. Han, E. Yoon, K. Lee, and C.-K. Kim, "High-performance electroplated solenoid-type integrated inductor (SI<sup>2</sup>) for RF applications using simple 3D surface micromachining technology," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Dec. 1998, pp. 544–547.

- [19] J.-B. Yoon, B.-K. Kim, C.-H. Han, E. Yoon, and C.-K. Kim, "Surface micromachined solenoid on-Si and on-glass inductors for RF applications," *IEEE Electron Device Lett.*, vol. 20, pp. 487–489, Sept. 1999.

- [20] Y. E. Chen, Y. K. Yoon, J. Laskar, and M. Allen, "A 2.4 GHz integrated CMOS power amplifier with micromachined inductors," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 2001, pp. 523–526.

- [21] B.-K. Kim, B.-K. Ko, and K. Lee, "Monolithic planar RF inductor and waveguide structures on silicon with performance comparable to those in GaAs MMIC," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Dec. 1995, pp. 717–720.

- [22] J. W. M. Rogers, V. Levenets, C. A. Pawlowicz, N. G. Tarr, T. J. Smy, and C. Plett, "Post-processed Cu inductors with application to a completely integrated 2-GHz VCO," *IEEE Trans. Electron Devices*, vol. 48, pp. 1284–1287, June 2001.

- [23] J. Y. Park and M. G. Allen, "Micromachined high  $Q$  inductors for high frequency applications," *Proc. SPIE*, vol. 3514, pp. 218–228, Sept. 1998.

- [24] —, "Packaging-compatible high  $Q$  microinductors and microfilters for wireless applications," *IEEE Trans. Adv. Packag.*, vol. 22, pp. 207–213, May 1999.

- [25] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "High-performance three-dimensional on-chip inductors fabricated by novel micromachining technology for RF MMIC," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1999, pp. 1523–1526.

- [26] J. Y. Park and M. G. Allen, "High  $Q$  spiral-type microinductors on silicon substrates," *IEEE Trans. Magn.*, vol. 35, pp. 3544–3546, Sept. 1999.

- [27] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "Monolithic high- $Q$  overhang inductors fabricated on silicon and glass substrates," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Dec. 1999, pp. 753–756.

- [28] D. J. Young and B. E. Boser, "A micromachined-based RF low-noise voltage-controlled oscillator," in *IEEE Custom Integrated Circuits Conf. Tech. Dig.*, May 1997, pp. 431–434.

- [29] A. Dec and K. Suyama, "Micromachined electro-mechanically tunable capacitors and their applications to RF IC's," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 2587–2596, Dec. 1998.

- [30] J.-B. Yoon and C. T.-C. Nguyen, "A high- $Q$  tunable micromechanical capacitor with movable dielectric for RF applications," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Dec. 2000, pp. 489–492.

- [31] H.-T. Kim, J.-H. Park, Y.-K. Kim, and Y. Kwon, "Millimeter-wave micromachined tunable filters," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 1999, pp. 1235–1238.

- [32] G. E. Ponchak, A. Margomenos, and L. P. B. Katehi, "Low-loss CPW on low-resistivity Si substrates with a micromachined polyimide interface layer for RFIC interconnects," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 866–870, May 2001.

- [33] H.-T. Kim, S. Jung, J.-H. Park, C.-W. Baek, Y.-K. Kim, and Y. Kwon, "A new micromachined overlay CPW structure with low attenuation over wide impedance ranges and its application to low-pass filters," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 1634–1639, Sept. 2001.

- [34] T. L. Willke and S. S. Gearhart, "LIGA micromachined planar transmission lines and filters," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1681–1688, Oct. 1997.

- [35] C.-M. Nam and Y.-S. Kwon, "High-performance planar inductor on thick oxidized porous silicon (OPS) substrate," *IEEE Microwave Guided Wave Lett.*, vol. 7, pp. 236–238, Aug. 1997.

- [36] H.-S. Kim, D. Zheng, A. J. Becker, and Y.-H. Xie, "Spiral inductors on Si/p+ substrates with resonant frequency of 20 GHz," *IEEE Electron Device Lett.*, vol. 22, pp. 275–277, June 2001.

- [37] C.-M. Nam and Y.-S. Kwon, "Coplanar waveguides on silicon substrate with thick oxidized porous silicon (OPS) layer," *IEEE Microwave Guided Wave Lett.*, vol. 8, pp. 369–371, Nov. 1998.

- [38] H. Guckel, "High-aspect-ratio micromachining via deep X-ray lithography," *Proc. IEEE*, vol. 86, pp. 1586–1593, Aug. 1998.

- [39] A. B. Frazier and M. G. Allen, "Metallic microstructures fabricated using photosensitive polyimide electroplating molds," *J. Microelectromech. Syst.*, vol. 2, pp. 87–94, June 1993.

- [40] G. Engelmann, O. Ehrmann, J. Simon, and H. Reichl, "Fabrication of high depth-to-width aspect ratio microstructures," in *Proc. IEEE Microelectromech. Syst.*, Feb. 1992, pp. 93–98.

- [41] B. Loeschel, A. Maciossek, and M. Rothe, "Application of ultraviolet depth lithography for surface micromachining," *J. Vac. Sci. Technol. B, Microelectron.*, vol. 13, pp. 2934–2939, Nov./Dec. 1995.

- [42] K. Y. Lee, N. LaBianca, S. A. Rishton, S. Zolgharnain, J. D. Gelorme, J. Shaw, and T. H.-P. Chang, "Micromachining applications of a high resolution ultrathick photoresist," *J. Vac. Sci. Technol. B, Microelectron.*, vol. 13, pp. 3012–3016, Nov./Dec. 1995.

- [43] R. C. Alford, R. E. Stengel, D. H. Weisman, and G. W. Marlin, "Method of forming a three-dimensional integrated inductor," U.S. Patent 6008 102, Dec. 28, 1999.

- [44] J.-B. Yoon, J.-D. Lee, C.-H. Han, E. Yoon, and C.-K. Kim, "Multilevel microstructure fabrication using single-step 3D photolithography and single-step electroplating," *Proc. SPIE*, vol. 3512, pp. 358–366, Sept. 1998.

- [45] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "Monolithic integration of 3-D electroplated microstructures of unlimited number of levels using planarization with a sacrificial metallic mold (PSMM)," in *IEEE Int. MEMS Conf. Tech. Dig.*, Jan. 1999, pp. 624–629.

- [46] Y.-S. Choi, J.-B. Yoon, B.-I. Kim, E. Yoon, and C.-H. Han, "Fabrication of a solenoid-type microwave transformer," in *Transducers'01*, pp. 1564–1567.

- [47] J.-B. Yoon, B.-I. Kim, Y.-S. Choi, and E. Yoon, "3-D lithography and metal surface micromachining for RF and microwave MEMS," in *IEEE Int. MEMS Conf. Tech. Dig.*, Jan. 2002, pp. 673-676.

- [48] J.-D. Lee, J.-B. Yoon, J.-K. Kim, H.-J. Chung, C.-S. Lee, H.-D. Lee, H.-J. Lee, C.-K. Kim, and C.-H. Han, "A thermal inkjet printhead with a monolithically fabricated nozzle plate and an ink feed hole self-aligned with the front pattern," *J. Microelectromech. Syst.*, vol. 8, pp. 229-236, Sept. 1999.

- [49] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "Novel two-step baking process for high-aspect-ratio photolithography with conventional positive thick photoresist," *Proc. SPIE*, vol. 3512, pp. 316-325, Sept. 1998.

- [50] H. M. Greenhouse, "Design of planar rectangular microelectronic inductors," *IEEE Trans. Parts, Hybrids, Packag.*, vol. PHP-10, pp. 101-109, June 1974.

- [51] J.-B. Yoon, Y.-S. Choi, B.-I. Kim, Y. Eo, and E. Yoon, "CMOS-compatible, surface micromachined, suspended spiral inductors on standard silicon for multi-GHz silicon RF IC's," *IEEE Electron Device Lett.*, vol. 23, pp. 591-593, Oct. 2002.

- [52] J. Craninckx and M. S. J. Steyaert, "A 1.8-GHz CMOS low-phase-noise voltage-controlled oscillator with prescaler," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1474-1482, Dec. 1995.

**Jun-Bo Yoon** (S'92-A'99-M'01) received the B.S. (*summa cum laude*), M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1993, 1995, and 1999, respectively. His doctoral research concerned the development of the three-dimensional microstructure technology (3D MEMS) for microfluidic systems and integrated inductors.

From 1999 to 2000, he was with The University of Michigan at Ann Arbor, as a Post-Doctoral Research Fellow, where he demonstrated a movable dielectric tunable micromechanical capacitor for RF applications. In 2000, he returned as a Research Assistant Professor to the Department of Electrical Engineering, KAIST, where he is currently an Assistant Professor. His research interests include microfabrication and nanofabrication (3-D microstructure and nanostructure) technologies, micro/nanosensors and actuators, optical MEMS, bio MEMS, and RF/microwave MEMS.

Dr. Yoon was the recipient of the Third-Place Award of the Student Paper Competition presented at the IEEE Microwave Theory and Techniques Society (IEEE MTT-S) International Microwave Symposium (IMS) in June 1999.

**Byeong-Il Kim** (A'01-M'01) received the B.S. and M.S. degrees in semiconductor engineering from Chungbuk National University, Cheong-ju, Korea, in 1997 and 1999, respectively.

He is currently a Research Engineer performing research and processes for RF device using the 3D MEMS Process at the Korea Advanced Institute of Science and Technology (KAIST). He was with the Research and Development Center, Korea Sangshin Electric Company Ltd., where he was engaged in research and processes on film bulk acoustic resonators (FBARs). His current research interests are fully IC compatible monolithically integrated RF device using the 3D MEMS Process.

**Yun-Seok Choi** was born in Busan, Korea. He received the B.S. degree in electronics engineering from the Busan National University, Busan, Korea, in 1997, the M.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1999, and is currently working toward the Ph.D. degree at KAIST.

His research interests include modeling of RF passive components and 3-D microstructure fabrication technology.

**Euisik Yoon** (S'80-M'82) received the B.S. and M.S. degrees in electronics engineering from the Seoul National University, Seoul, Korea, in 1982 and 1984, respectively, and Ph.D. degree in electrical engineering from The University of Michigan at Ann Arbor, in 1990.

From 1990 to 1994, he was with the Fairchild Research Center, National Semiconductor Corporation, Santa Clara, CA, where he was engaged in research on deep-submicrometer CMOS integration and advanced gate dielectrics. From 1994 to 1996, he was a Member of Technical Staff with Silicon Graphics Inc., Mountain View, CA, where he was involved with the design of the MIPS microprocessor R4300I and the RCP 3-D graphic coprocessor. In 1996, he joined the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, where he is currently an Associate Professor. His current research interests are MEMS, integrated microsystems, and very large scale integration (VLSI) circuit design.

Dr. Yoon has served on various Technical Program Committees including the Microprocesses and Nanotechnology Conference, International Sensor Conference, and IEEE Asia-Pacific Conference on Application Specific Integrated Circuits (ASICs). He currently serves on the IEEE International Solid-State Circuits Conference (ISSCC) Program Committee and Transducers Technical Program Committee.